Logic ba trạng thái

Giao diện

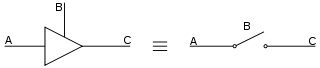

Logic ba trạng thái (tiếng Anh: three-state logic hay tri-state logic) trong điện tử học là mạch logic có ngõ ra có bố trí trạng thái thứ ba là trạng thái trở kháng cao cộng với mức logic 0 và 1, nhằm có thể ngăn chặn ngõ ra này tác động (tức là điều khiển sự truyền đưa các mức logic ra của mạch) lên đường truyền tín hiệu.[1][2]

| INPUT | OUTPUT | |

| A | B | C |

| 0 | 1 | 0 |

| 1 | 1 | |

| X | 0 | Z (high impedance) |

Hoạt động

[sửa | sửa mã nguồn]Logic ba trạng thái (tiếng Anh: three-state logic hay tri-state logic) trong điện tử học là mạch logic có ngõ ra có bố trí trạng thái thứ ba là trạng thái trở kháng cao cộng với mức logic 0 và 1, nhằm có thể ngăn chặn ngõ ra này tác động (tức là điều khiển sự truyền đưa các mức logic ra của mạch) lên đường truyền tín hiệu.[1][2]

Ứng dụng

[sửa | sửa mã nguồn]Tham khảo

[sửa | sửa mã nguồn]- ^ a b Charles C. Lin (2003). What's a Tri-state Buffer?. Truy cập 22/05/2017.

- ^ a b Winfield Hill and Paul Horowitz (1989). The Art of Electronics. Cambridge University Press. tr. 495–497. ISBN 0-521-37095-7.

Xem thêm

[sửa | sửa mã nguồn]Wikimedia Commons có thêm hình ảnh và phương tiện truyền tải về Logic ba trạng thái.

Liên kết ngoài

[sửa | sửa mã nguồn]- Special-output Gates on All About Circuits

- What's a Tri-state Buffer?

- Principle of Tristate Multiplexing